Le passage à Zen 4 n'aura pas lieu cette année, mais AMD a déjà une réponse pour le projet Alder Lake d'Intel Alder Lake d'Intel. Comme annoncé au Computex plus tôt cet été, AMD va mettre à niveau ses processeurs Zen 3 avec la fonction 3D V-Cache au début de l'année 2022, ce qui devrait suffire à égaliser les chances face à Intel, du moins jusqu'au lancement de la prochaine génération, fin 2022. Lors du symposium annuel Hot Chips, AMD a récemment fourni plus de détails sur le fonctionnement de 3D V-Cache et a également offert un aperçu de ses futures applications d'empilage 3D.

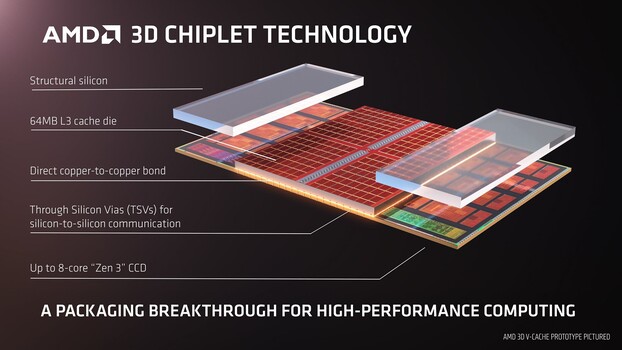

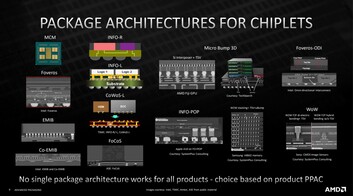

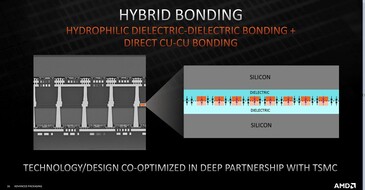

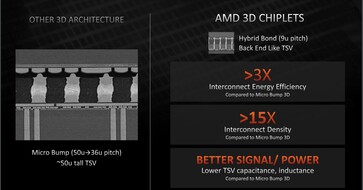

AMD met en œuvre un boîtier Micro Bump 3D chiplet de 9 microns pour le V-Cache through silicon via (TSV). Bien qu'il ne soit plus fin que d'un micron par rapport à la technologie Foveros 3D d'Intel qui sera utilisé pour produire les processeurs Alder Lake, les Micro Bumps d'AMD sont censés offrir une efficacité énergétique d'interconnexion plus de 3 fois supérieure, une densité d'interconnexion et une capacitance/inductance 15 fois supérieures. La technologie TSV actuelle qui fait office de connexion verticale inter-wafer ou inter-die n'offre pas trop de liaisons, mais, à l'avenir, le pas des TSV sera de plus en plus affiné, permettant des conceptions d'empilement 3D plus complexes. V-Cache, par exemple, permet une communication complète silicium à silicium (DRAM sur CPU / CPU sur CPU) via des liaisons directes cuivre à cuivre. Cela permet d'ajouter 64 Mo de cache L3 à la quantité existante, ce qui est censé apporter une augmentation des performances de 15 % dans les jeux et de 19 % dans les applications de création de contenu.

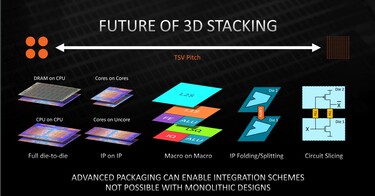

Des pas TSV plus fins permettront des techniques d'empilement 3D complexes, notamment IP sur IP (cœurs sur cœurs / cœurs sur uncore), macro sur macro (SoCs sur SoCs), et même, à terme, le pliage/séparation d'IP et le découpage de circuits. Les besoins en énergie seront également divisés par plus de trois. Nous verrons probablement la première application de la technique de l'IP sur IP avec les RDNA2 empilés sur les cœurs du Zen 4

Leaked AMD documents confirm integrated GPUs for next-generation Socket AM5 processors

Top 10

» Le Top 10 des PC portables multimédia

» Le Top 10 des PC portables de jeu

» Le Top 10 des PC portables de jeu légers

» Le Top 10 des ordinateurs portables bureautiques

» Le Top 10 des PC portables bureautiques premium/professionnels

» Le Top 10 des Stations de travail mobiles

» Le Top 10 des Ultraportables

» Le Top 10 des Ultrabooks

» Le Top 10 des Convertibles

» Le Top 10 des Tablettes

» Le Top 10 des Tablettes Windows

» Le Top 10 des Smartphones

» Le Top 10 des PC Portables á moins de 300 euros

» Le Top 10 des PC Portables á moins de 500 euros

» Le Top 25 des meilleurs écrans d'ordinateurs