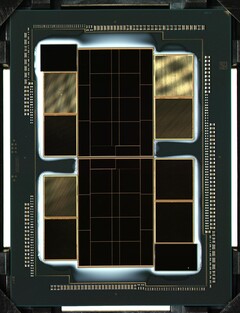

Raja Koduri, d'Intel, a récemment tweeté une photo d'une puce HPC Ponte Vecchio Xe à deux tuiles, affirmant qu'elle comprenait sept technologies avancées de silicium et la qualifiant de "chose de beauté". Ce GPU Xe HPC offre 16 clusters avec 128 unités d'exécution (EU) chacun et un total de 8 192 cœurs

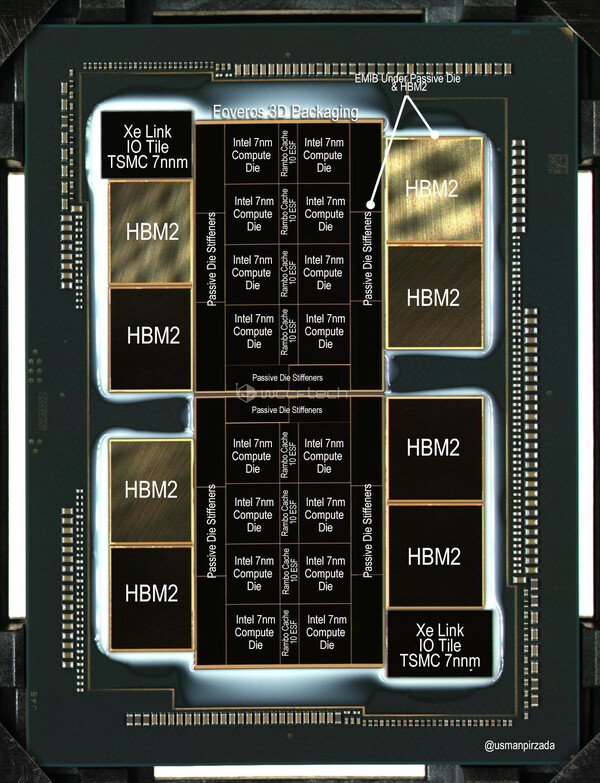

Bien que Raja n'ait pas exactement détaillé les sept technologies avancées en silicium auxquelles il faisait allusion, Wccftech a réussi à obtenir des annotations pour cette puce qui offrent plus d'informations. Wccftech affirme avoir vérifié cette annotation à partir d'au moins deux de ses sources. Selon la publication, les sept technologies avancées du silicium pourraient l'être :

- Processus 7 nm d'Intel

- Processus TSMC 7 nm

- Emballage Foveros 3D

- Pont d'interconnexion multi-matrices intégré (EMIB)

- Intel 10 nm Enhanced SuperFin process

- Rambo Cache

- HBM2 VRAM

Dans les coins supérieur gauche et inférieur droit, nous avons la tuile Xe Link I/O fabriquée selon le procédé TSMC 7 nm. Nous voyons également deux paires de matrices HBM2 de tailles différentes de chaque côté des tuiles de calcul. Les unités de calcul sont fabriquées sur le propre processus 7 nm d'Intel, ce qui signifie que nous voyons la nouvelle technologie de processus d'Intel pour la première fois dans la nature.

Au milieu de chacune des grappes de huit unités de calcul se trouve ce qui semble être le cache Rambo fabriqué sur le processus SuperFin amélioré de 10 nm d'Intel. Autour de chaque grappe, sur trois côtés, se trouvent des raidisseurs passifs qui ne contiennent aucune logique.

Wccftech note que sous les tuiles se trouve une puce de base de 10 nm tandis que l'interconnexion EMIB se trouve sous les raidisseurs de puce passifs et la mémoire HBM2. L'ensemble utilise la technologie de packaging Foveros 3D d'Intel, ce qui le rend beaucoup plus complexe qu'il n'y paraît.

M. Raja a déclaré que ce boîtier particulier est maintenant prêt à être mis sous tension. Ponte Vecchio sera lancé fin 2021 ou début 2022 et est principalement destiné aux centres de données et aux applications HPC telles que le supercalculateur Aurora exascale

À un moment donné, nous pourrions également voir cette technologie se propager jusqu'aux GPU grand public d'Intel. Actuellement, l'offre d'Intel en matière de dGPU grand public est le Xe DG1, le Xe HPG basé sur le DG2 étant attendu pour la fin de l'année.

Xe HPC ready for power on!

— Raja Koduri (@Rajaontheedge) January 26, 2021

7 advanced silicon technologies in a single package

Silicon engineers dream

Thing of beauty @intel pic.twitter.com/RF8Prsy05f

Source(s)

Top 10

» Le Top 10 des PC portables multimédia

» Le Top 10 des PC portables de jeu

» Le Top 10 des PC portables de jeu légers

» Le Top 10 des ordinateurs portables bureautiques

» Le Top 10 des PC portables bureautiques premium/professionnels

» Le Top 10 des Stations de travail mobiles

» Le Top 10 des Ultraportables

» Le Top 10 des Ultrabooks

» Le Top 10 des Convertibles

» Le Top 10 des Tablettes

» Le Top 10 des Tablettes Windows

» Le Top 10 des Smartphones

» Le Top 10 des PC Portables á moins de 300 euros

» Le Top 10 des PC Portables á moins de 500 euros

» Le Top 25 des meilleurs écrans d'ordinateurs