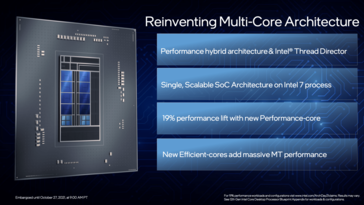

Après de nombreuses séries de fuitesc'est enfin arrivé. Intel a dévoilé la nouvelle gamme de processeurs Alder Lake-S de 12e génération pour ordinateurs de bureau. Au cours de la présentation, Marcus Kennedy, d'Intel, a donné un aperçu des caractéristiques d'Alder Lake et de la manière dont l'architecture hétérogène composée de processeurs Golden Cove Performance (P) et Gracemont Efficiency (E) fonctionne dans le système.

ISA hétérogène, désormais sur le bureau grand public

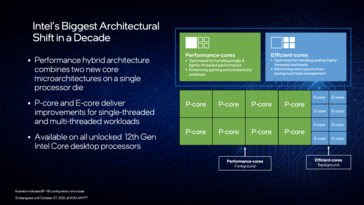

Selon Intel, les noyaux P sont optimisés pour les applications à un seul et léger thread comme les jeux et les tâches de productivité générale en avant-plan, tandis que les noyaux E sont orientés vers les charges de travail avec de nombreux threads. Les E-cores peuvent également aider à gérer les tâches d'arrière-plan, tandis que les P-cores se concentrent davantage sur les aspects liés aux performances. Cette approche n'est pas très différente de l'approche big.LITTLE adoptée par les processeurs ARM depuis des années.

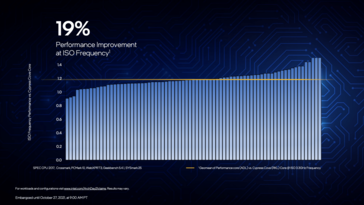

Intel a déclaré que ce changement d'architecture peut offrir jusqu'à 19 % d'amélioration par rapport à la génération précédente de cœurs Cypress Cove dans Rocket Lake à la même fréquence.

Top 10

» Le Top 10 des PC portables multimédia

» Le Top 10 des PC portables de jeu

» Le Top 10 des PC portables de jeu légers

» Le Top 10 des ordinateurs portables bureautiques

» Le Top 10 des PC portables bureautiques premium/professionnels

» Le Top 10 des Stations de travail mobiles

» Le Top 10 des Ultraportables

» Le Top 10 des Ultrabooks

» Le Top 10 des Convertibles

» Le Top 10 des Tablettes

» Le Top 10 des Tablettes Windows

» Le Top 10 des Smartphones

» Le Top 10 des PC Portables á moins de 300 euros

» Le Top 10 des PC Portables á moins de 500 euros

» Le Top 25 des meilleurs écrans d'ordinateurs

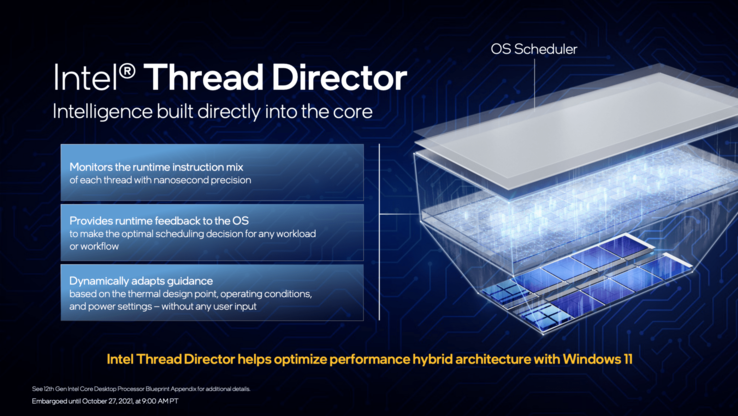

Intel Thread Director

Si les systèmes d'exploitation mobiles sont conçus dès le départ pour tenir compte des architectures hétérogènes, la situation est différente sur un ordinateur de bureau. C'est pourquoi Intel a mis au point sa propre méthode pour diriger les threads vers le cœur approprié. Baptisé Intel Thread Director, ce système permet au planificateur du système d'exploitation d'être conscient de la présence de différentes ISA sur le même SoC et de gérer efficacement les ressources. Intel a déclaré que Thread Director prend en compte plusieurs paramètres tels que le TDP, la puissance disponible, etc. et fournit un retour d'information continu à l'ordonnanceur du système d'exploitation avec une "précision de l'ordre de la nanoseconde".

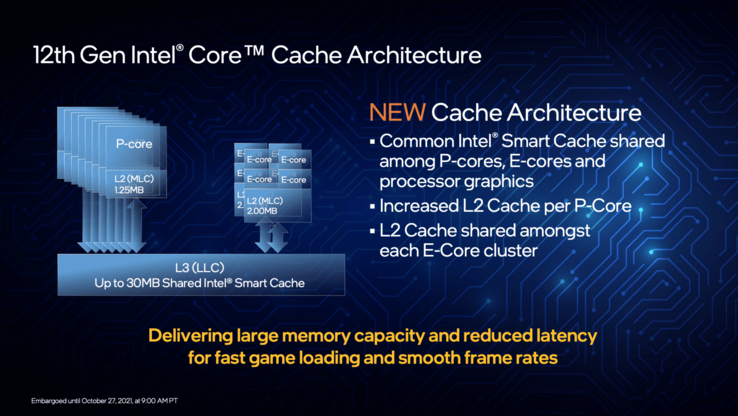

Cache L3 commun de 30 Mo pour les noyaux P et E

Compte tenu de l'utilisation de deux ISA, Intel a également retravaillé la topologie de son cache pour la 12e génération. Le Rocket Lake de 11e génération utilisait des cœurs Cypress Cove, qui étaient essentiellement des Sunny Cove de 10 nm ramenés à 14 nm. Cypress Cove proposait huit cœurs dotés chacun d'un cache L2 de 512 Ko et d'un cache L3 de 2 Mo. Avec Alder Lake, chaque cœur P dispose d'un cache L2 de 1,25 Mo, tandis que chaque cluster de cœurs E dispose d'un cache L2 partagé de 2 Mo. Nous pensons que cela signifie qu'un ensemble de quatre E-cores partagerait un seul cache L2, mais nous le confirmerons bientôt avec Intel.

Outre les caches L2 dédiés, Alder Lake dispose également d'un cache L3 partagé de 30 Mo pour les deux types de cœurs et le GPU intégré afin de réduire la latence. Bien qu'il ne s'agisse pas d'une comparaison directe, nous avons vu comment le cache L3 partagé offre des avantages immédiats en termes de performances dans le cas des processeurs AMD Ryzen 5000 Zen 3.

Caractéristiques de la plate-forme de 12e génération - Pas de PCIe Gen5 sur le chipset

Alder Lake est basé sur un processus SuperFin amélioré de 10 nm, désormais connu sous le nom d'Intel 7. Sur l'ordinateur de bureau, le Core i9-12900K offrira jusqu'à 16 cœurs et 24 threads - 8 cœurs P qui prennent en charge l'hyperthreading et 8 cœurs E qui ne le font pas.

Le processeur prend en charge la RAM DDR5-4800,et nous avons également vu plusieurs annonces de kits DDR5 de la part des équipementiers. Celadit, la mémoire DDR4-3200 fonctionne très bien aussi.

Les processeurs Alder Lake offrent également jusqu'à 16 voies de connectivité PCIe Gen5. Toutefois, les chipsets de la série 600 ne peuvent prendre en charge que 12 voies de PCIe Gen4. Les raisons exactes de la réduction de la connectivité PCIe Gen5 pour les chipsets de la série 600, y compris le chipset phare Z690, ne sont pas totalement claires. Il se peut qu'Intel ait pensé qu'une telle implémentation ferait grimper les prix, sans parler de la consommation d'énergie

Par ailleurs, même un GPU tel que le NVIDIA GeForce RTX 3090 peut difficilement saturer le PCIe Gen3 x16. Ceci étant dit, le stockage est un bon bénéficiaire de l'augmentation des E/S, donc nous pourrions voir quelques nouveaux disques NVMe qui peuvent éventuellement utiliser une bonne partie de la bande passante, qui, au cas où vous vous poseriez la question, est d'environ 128 Go/s agrégés sur 16 voies.

Au total, le chipset Z690 peut offrir jusqu'à 28 voies PCIe - 16 Gen3 et 12 Gen4. En outre, huit voies sont prévues pour la Direct Media Interface (DMI) 4.0. Pour ceux qui ne le savent pas, DMI est un terme fantaisiste pour désigner le lien entre le processeur et le concentrateur de contrôle de la plate-forme (PCH), c'est-à-dire le chipset (Northbridge et Southbridge, par exemple)

Il prend également en charge jusqu'à 4 ports USB 3.2 Gen2x2, 10 ports USB 3.2 Gen2, 10 ports USB 3.2 Gen1 et 14 ports USB 2.0. La connectivité ne devrait donc pas poser de problème. Enfin, il y a huit voies de ports SATA 6 Gb/s pour l'extension du stockage

Source(s)

Communiqué de presse d'Intel