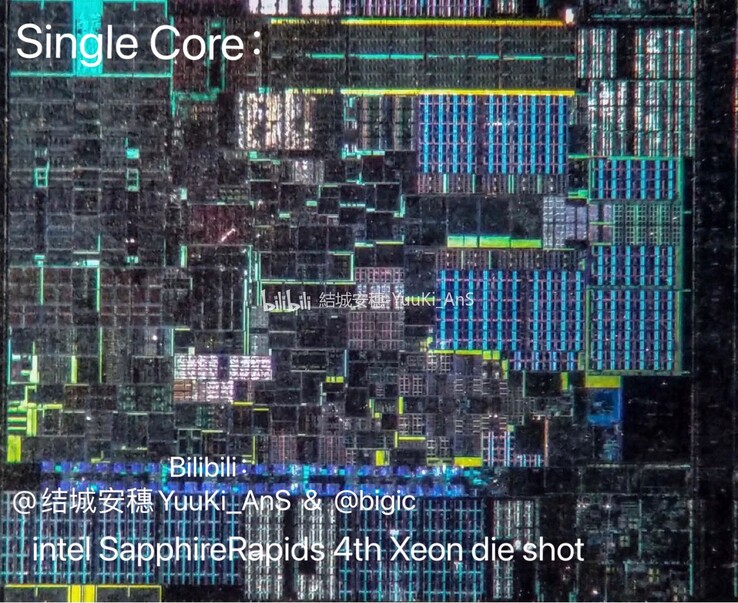

Tipster @AnsYuuki a publié ce qui semble être des clichés d'un prochain processeur Intel Sapphire Rapids Xeon. Nous sommes face à ce qui est probablement la variante haut de gamme, avec 56 des 60 cœurs activés - 14 sur 15 sur chacun des 4 chiplets MCM.

En utilisant le Golden Cove avec une lithographie en 10 nm, les nouvelles puces Xeon présenteront un IPC nettement supérieur et une consommation d'énergie inférieure, grâce à une architecture repensée et à un rétrécissement de la matrice. Cela signifie qu'Intel pourrait disposer d'une pièce compétitive pour faire face à la prochaine puce EPYC Genoa d'AMD basée sur Zen 4 EPYC Genoa.

Bien que le Xeon basé sur Golden Cove ne compte que 56 cœurs, soit beaucoup moins que l'EPYC Genoa, Intel a un atout dans sa manche : une meilleure prise en charge des configurations multi-socket. Une configuration EPYC Genoa à deux sockets pourrait comporter 192 cœurs, ce qui n'est pas négligeable

Cependant, les utilisateurs professionnels haut de gamme pourraient empiler jusqu'à 8 puces Sapphire Rapids de 4e génération dans une configuration multi-socket, pour un nombre de cœurs bien plus élevé par rack de serveur. En dehors du passage au 10 nm, les nouvelles puces prendront en charge la future DDR5 RAM ainsi que la norme PCIe 5.0

Source(s)

Top 10

» Le Top 10 des PC portables multimédia

» Le Top 10 des PC portables de jeu

» Le Top 10 des PC portables de jeu légers

» Le Top 10 des ordinateurs portables bureautiques

» Le Top 10 des PC portables bureautiques premium/professionnels

» Le Top 10 des Stations de travail mobiles

» Le Top 10 des Ultraportables

» Le Top 10 des Ultrabooks

» Le Top 10 des Convertibles

» Le Top 10 des Tablettes

» Le Top 10 des Tablettes Windows

» Le Top 10 des Smartphones

» Le Top 10 des PC Portables á moins de 300 euros

» Le Top 10 des PC Portables á moins de 500 euros

» Le Top 25 des meilleurs écrans d'ordinateurs