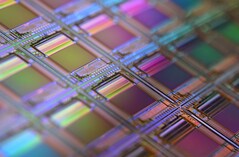

Des chercheurs créent un prototype de puce de contrôle 2T1R pour l'informatique neuromorphique

Et si votre disque dur pouvait penser avec vos données ? Au lieu de simplement stocker des fichiers, imaginez qu'il traite les informations et y répond exactement là où elles sont conservées. C'est le principe de l'informatique en mémoire, une évolution croissante de l'architecture qui rapproche la logique de la mémoire pour améliorer l'efficacité.

Des chercheurs du Forschungszentrum Jülich et de l'université de Duisburg-Essen ont présenté une nouvelle conception basée sur les memristors 2T1R qui pourrait prendre en charge ce changement et permettre une IA et un matériel de pointe plus efficaces sur le plan énergétique.

Publiée sur arXivla conception intègre deux transistors et un memristor par cellule, avec une régulation du courant destinée à supprimer les courants de cheminement furtif, un défi connu dans les réseaux de memristors. Contrairement à la mémoire conventionnelle, la conception proposée met à la terre les deux bornes du memristor lorsqu'elles sont inactives - une stratégie qui peut contribuer à améliorer la stabilité du signal et à réduire les fuites.

L'architecture est conçue pour prendre en charge la multiplication vectorielle matricielle analogique (VMM), une fonction essentielle de l'apprentissage automatique, en contrôlant la conductance des memristors à l'aide de CNA intégrés, de signaux PWM et de circuits de courant régulés. Un réseau de test 2×2 a été mis en œuvre avec succès en utilisant la technologie CMOS standard 28 nm.

En s'attaquant aux problèmes de masse virtuelle et aux effets de résistance des fils, l'architecture vise à améliorer la prévisibilité des performances et à réduire la consommation d'énergie. Compatible avec le contrôle RISC-V et l'interface numérique, la conception 2T1R pourrait jeter les bases de puces neuromorphiques évolutives, permettant une accélération de l'IA plus rapide et plus compacte directement dans la mémoire.

Votre disque dur n'est peut-être pas encore en train de penser, mais l'architecture qui sous-tend cette vision prend déjà forme dans le silicium, laissant entrevoir un avenir d'IA plus rapide et intégrée à la mémoire.

Pour obtenir tous les détails techniques et les résultats, consultez la prépublication arXiv complète de (PDF).

Source(s)

Top 10

» Le Top 10 des PC portables multimédia

» Le Top 10 des PC portables de jeu

» Le Top 10 des PC portables de jeu légers

» Le Top 10 des ordinateurs portables bureautiques

» Le Top 10 des PC portables bureautiques premium/professionnels

» Le Top 10 des Stations de travail mobiles

» Le Top 10 des Ultraportables

» Le Top 10 des Ultrabooks

» Le Top 10 des Convertibles

» Le Top 10 des Tablettes

» Le Top 10 des Tablettes Windows

» Le Top 10 des Smartphones

» Le Top 10 des PC Portables á moins de 300 euros

» Le Top 10 des PC Portables á moins de 500 euros

» Le Top 25 des meilleurs écrans d'ordinateurs