La fuite AMD Zen 7 "Florence" annonce des puces Epyc à 288 cœurs et des gains d'efficacité importants pour les ordinateurs portables

La plate-forme serveur de nouvelle génération d'AMD pourrait faire passer le nombre de cœurs de processeurs grand public à un niveau encore impensable il y a quelques années, les utilisateurs de stations de travail et d'ordinateurs de bureau haut de gamme pouvant potentiellement bénéficier des mêmes blocs de construction.

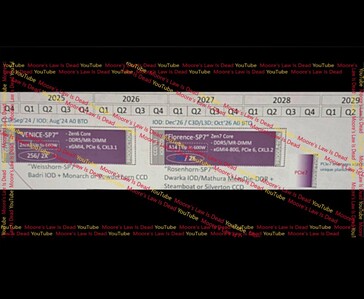

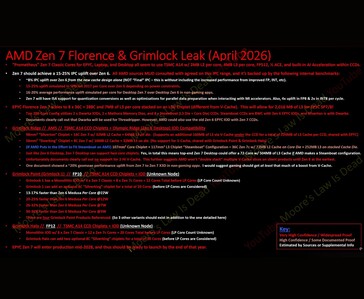

Selon une série de diapositives partagées par Tom, l'animateur de Moore's Law Is Dead sur YouTube, connu pour ses fuites de matériel, Le fleuron Zen 7 EPYC d'AMDd'AMD, dont le nom de code est Florence, repose sur deux matrices d'E/S "Dwarka" et deux matrices de mémoire "Mathura", toutes deux nommées d'après d'anciennes villes indiennes d'une importance historique et spirituelle considérable, associées à un maximum de huit CCD Steamboat à 36 cœurs, ce qui donne 288 cœurs par socket.

Chaque CCD Steamboat combine un processeur Zen 7 sur le nœud A14 de Nœud A14 de TSMC avec un chiplet de cache L3 séparé sur N4P, empilé en dessous plutôt qu'au-dessus comme avec le 3D V-Cache existant. Les diapositives mentionnent 7 Mo de L3 par cœur, une interface PCIe 6 + CXL 3.2, une vitesse de liaison xGMI4-80G et un TDP pouvant atteindre 600 W.

Top 10

» Le Top 10 des PC portables multimédia

» Le Top 10 des PC portables de jeu

» Le Top 10 des PC portables de jeu légers

» Le Top 10 des ordinateurs portables bureautiques

» Le Top 10 des PC portables bureautiques premium/professionnels

» Le Top 10 des Stations de travail mobiles

» Le Top 10 des Ultraportables

» Le Top 10 des Ultrabooks

» Le Top 10 des Convertibles

» Le Top 10 des Tablettes

» Le Top 10 des Tablettes Windows

» Le Top 10 des Smartphones

» Le Top 10 des PC Portables á moins de 300 euros

» Le Top 10 des PC Portables á moins de 500 euros

» Le Top 25 des meilleurs écrans d'ordinateurs

Il est indiqué que la puce d'E/S de Dwarka et la puce de mémoire de Mathura utiliseront toutes deux le processus N3C de TSMC Le processus N3C de TSMC. Une diapositive montre une sortie de bande A0 prévue pour octobre 2026, avec une production ciblée pour la mi-2028 et un lancement vers la fin de cette année. Une autre entrée de la feuille de route indique qu'une plateforme PCIe Gen 7 arrivera vers 2029, peut-être en tant que rafraîchissement de mi-génération sur un nouveau socket.

Les acheteurs de plates-formes AMD de la génération actuelle n'auront peut-être pas besoin de changer de socket pour bénéficier du prochain saut architectural, et les utilisateurs d'ordinateurs portables en particulier devraient bénéficier de certains des gains les plus importants. Les documents divulgués indiquent que les CCD Zen 7 sont rétrocompatibles avec les IO dies Kedar et Weisshorn de la génération précédente, tandis que les CCD Silverton fonctionneront avec les IOD Badri, Kedar, Puri et Dwarka dans les emballages SP7 et SP8, avec une prise en charge de 2, 4, 6 ou 8 CCD par socket. La prise en charge de Threadripper et HEDT via l'IOD Dwarka est explicitement mentionnée.

Un tableau de performances séparé pour les chiplets Silverton et Silverking orientés vers le consommateur indique des gains par cœur de 16 à 20 % pour des charges de travail de serveur inférieures à 9 W, et de 30 à 36 % dans des scénarios d'APU client de 3 W/cœur, indiquant des améliorations d'efficacité particulièrement fortes pour les ordinateurs portables minces et légers.

Tom suppose que la largeur similaire du CCD Steamboat à 36 cœurs par rapport au Silverton à 16 cœurs pourrait théoriquement permettre à AMD d'intégrer deux Steamboat sur AM5 pour obtenir une puce de bureau à 72 cœurs, bien qu'aucune diapositive divulguée ne confirme un tel produit. L'auteur de la fuite lui-même suggère qu'une telle pièce viserait plus probablement les clients embarqués que le marché des bricoleurs.

Regardez sa vidéo, en lien ci-dessous, pour un aperçu détaillé des informations divulguées et de son point de vue.