Après avoir démontré avec succès l'efficacité d'une conception de module multi-puces (MCM) du côté du CPU, AMD pourrait très bien se réjouir de répéter le succès du côté du GPU de l'équation également. Un brevet intitulé"GPU Chiplets using High Bandwidth Crosslinks" déposé en 2019 et maintenant disponible sur le site web de l'Office des brevets en ligne (FPO) indique qu'AMD a quelques astuces dans sa manche pour passer efficacement de la conception monolithique classique.

Voici le résumé du brevet,

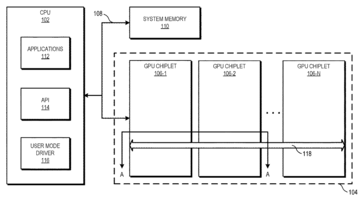

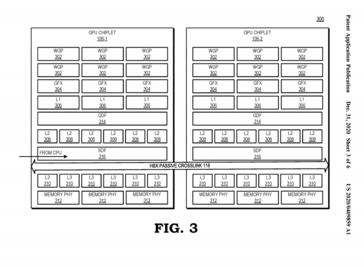

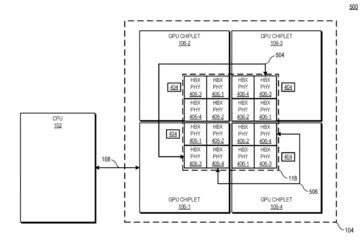

Un système à puces comprend une unité centrale de traitement (CPU) couplée de manière communicante à une première puce d'un réseau de puces GPU. Le réseau de puces GPU comprend la première puce GPU couplée à l'unité centrale par un bus et une deuxième puce GPU couplée à la première par une liaison passive. La réticulation passive est une puce d'interposition passive dédiée aux communications inter-puces et qui partitionne les fonctionnalités des systèmes sur puce (SoC) en groupes de puces fonctionnelles plus petits"

Dans la demande de brevet, AMD note que les puces monolithiques sont de plus en plus coûteuses à fabriquer. Elle note également que les charges de travail parallèles dans les GPU sont difficiles à répartir correctement sur plusieurs puces et à synchroniser la mémoire entre elles. De plus, la plupart des applications sont écrites en gardant à l'esprit un seul GPU. Par conséquent, le défi consiste à préserver autant que possible le modèle de programmation actuel tout en offrant une conception de puces pour réduire les coûts de fabrication et améliorer les rendements.

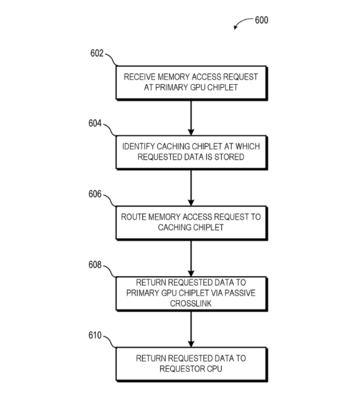

Pour surmonter ces préoccupations, le brevet d'AMD envisage d'utiliser le premier GPU de la série des chiplettes pour le coupler directement au CPU. Les autres puces GPU de la série seraient ensuite couplées au GPU primaire par l'intermédiaire d'une réticulation passive à large bande passante (HBPC). La HBPC est essentiellement une puce d'interposition passive dédiée à la communication inter-puces à travers le SoC.

En ce qui concerne la synchronisation de la mémoire, le brevet indique que bien que chaque puce GPU dispose de son propre cache de dernier niveau (LLC), tous ces LLC sont couplés de manière à assurer la cohérence entre toutes les puces GPU. Étant donné que seule la puce GPU primaire reçoit des requêtes du CPU, l'ensemble du complexe apparaît toujours monolithique au CPU et, par conséquent, au système d'exploitation.

À l'heure actuelle, AMD propose déjà des conceptions multi-GPU sur une seule carte. Auparavant, nous avons vu la Radeon R9 295X2 d'AMD et la Radeon Pro Duo. La plus récente, la Radeon Pro Vega II Duo, est une exclusivité du Mac Pro Apple et comporte deux Radeon VII avec 64 unités de calcul (CU) chacune reliée par un lien Infinity Fabric.

En 2018, David Wang, vice-président du Radeon Technologies Group (RTG) d'AMD, a déclaré qu'à moins qu'un ensemble multi-GPU ne soit rendu invisible, les éditeurs de logiciels indépendants pourraient se montrer réticents. Cependant, il s'est également montré optimiste en affirmant que"tout est possible".

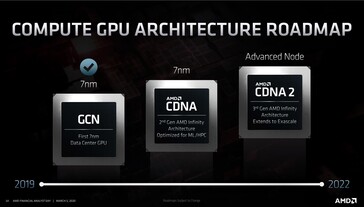

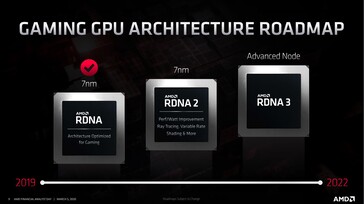

Aujourd'hui, on ne sait pas quand nous verrons une telle conception en chair et en os. Les feuilles de route officielles de la CDNA et de la RDNA n'indiquent qu'un "nœud avancé" pour 2022, il est donc probable que nous ne verrons pas de conception de CDNA 2 ou de RDNA 3 avec des modules multi-puces (MCM)

Cela étant dit, la concurrence montre déjà des tendances similaires, Intel et NVIDIA cherchant à proposer des pièces MCM avec le Xe HP Arctic Sound et le Hopper, respectivement

Source(s)

Top 10

» Le Top 10 des PC portables multimédia

» Le Top 10 des PC portables de jeu

» Le Top 10 des PC portables de jeu légers

» Le Top 10 des ordinateurs portables bureautiques

» Le Top 10 des PC portables bureautiques premium/professionnels

» Le Top 10 des Stations de travail mobiles

» Le Top 10 des Ultraportables

» Le Top 10 des Ultrabooks

» Le Top 10 des Convertibles

» Le Top 10 des Tablettes

» Le Top 10 des Tablettes Windows

» Le Top 10 des Smartphones

» Le Top 10 des PC Portables á moins de 300 euros

» Le Top 10 des PC Portables á moins de 500 euros

» Le Top 25 des meilleurs écrans d'ordinateurs